다층접속 나노소재 및 고집적 공정기술

강남기 전자부품연구원 전자소재패키징연구센터 수석연구원

박성대 전자부품연구원 전자소재패키징연구센터 책임연구원

이우성 전자부품연구원 전자소재패키징연구센터 책임연구원

1. 서 론

정보통신산업의 발달에 따라 단말기 및 관련 전자부품들의 경박단소화에 대한 요구가 급증하고 있다. 특히 유기소재를 기반으로 하는 인쇄회로기판 및 패키징 분야에서는 3차원 고집적 패키징을 위하여 빌드업(Build-up) 기판기술, 임베디드(Embedded) 능·수동소자 기술, 및 마이크로비아기술 등이 활발히 연구되어  상용화가 이루어지고 있다. 이러한 추세는 세라믹 다층기판 및 세라믹-고분자 복합 기판에 있어서도 필수적으로 확보해야할 요소기술들이다. 본고에서 기술하고자하는 다층접속 나노소재는 세라믹-고분자 기반의 High Density Interconnection (HDI) 기판 제작을 위하여 사용되는 소재로써, 다층화시 층간의 전기적 접속 또는 패키지된 IC의 방열을 목적으로 이용되는 소재이다. 크게 에칭형, 도금형, 페이스트형의 소재들로 구분할 수 있으며, 특히 저가의 페이스트형 소재에 대한 연구가 활발히 진행되고 있다. 한편 에칭을 이용하지 않는 미세회로 도금기술을 기반으로 한 3차원 고집적 공정기술 또한 주목할 만한 분야이며, 특히 Ajinomoto사의 본딩 필름을 이용하여 고집적화를 시도하는 연구들이 국내에서도 활발히 진행되고 있다. 본고에서는 마이크로비아용 층간접속 도체를 형성하는 페이스트 소재기술과 본딩 필름을 이용한 고집적 공정기술의 개발동향에 대하여 간략히 소개하고자 한다.

상용화가 이루어지고 있다. 이러한 추세는 세라믹 다층기판 및 세라믹-고분자 복합 기판에 있어서도 필수적으로 확보해야할 요소기술들이다. 본고에서 기술하고자하는 다층접속 나노소재는 세라믹-고분자 기반의 High Density Interconnection (HDI) 기판 제작을 위하여 사용되는 소재로써, 다층화시 층간의 전기적 접속 또는 패키지된 IC의 방열을 목적으로 이용되는 소재이다. 크게 에칭형, 도금형, 페이스트형의 소재들로 구분할 수 있으며, 특히 저가의 페이스트형 소재에 대한 연구가 활발히 진행되고 있다. 한편 에칭을 이용하지 않는 미세회로 도금기술을 기반으로 한 3차원 고집적 공정기술 또한 주목할 만한 분야이며, 특히 Ajinomoto사의 본딩 필름을 이용하여 고집적화를 시도하는 연구들이 국내에서도 활발히 진행되고 있다. 본고에서는 마이크로비아용 층간접속 도체를 형성하는 페이스트 소재기술과 본딩 필름을 이용한 고집적 공정기술의 개발동향에 대하여 간략히 소개하고자 한다.

2. 나노금속분말을 이용한 층간접속소재

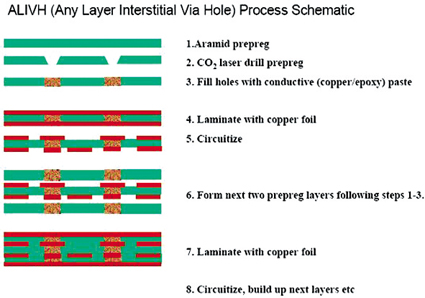

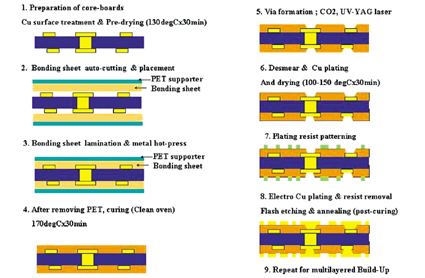

반도체 집적회로의 초다핀화에 대응하는 HDI는 일반 Build-up 기판과 달리 마이크로비아의 사용을 지향하며, 특히 ‘Sta cked via’의 형성을 기본으로 하는데, 기존의 Staggered via에 비해 짧은 전도 path를 형성하므로 고집적화에 유리하다. 마이크로비아의 형성기술은 크게 네 가지 범주로 구분할 수 있는데, Photovia process, Plasma-via process, Laser-via process, Paste-via process 등이 있으며, 일부 폴리이미드 필름을 사용하는 기술을 제외하면 마이크로비아의 크기는 100~150㎛, 미세도선의 선폭은 75~100㎛ 수준을 보이고 있다. 전도성 페이스트로 비아를 충진하는 방법은, 주로 Ag, Cu 금속분말을 열경화성 수지와 혼합하여 제작된 페이스트를 스크린 인쇄방법 등을 이용하여 레이저에 의해 형성된 마이크로비아를 충진하는 방법이다. 다수의 일본업체들은 이미 상당 수준의 층간접속 페이스트 기반의 HDI 기술을 개발하여 제품을 출시하고 있다. 대표적인 기술로서 Matsushita의 ALIVH, Denso의 PALAP, DNP의 B2it 등을 들 수 있으며, 각 기술별로 고유의 특징을 보유하고 있다. 대표적인 페이스트 기반 HDI 기술의 공정도를 그림 1에 나타내었다.

cked via’의 형성을 기본으로 하는데, 기존의 Staggered via에 비해 짧은 전도 path를 형성하므로 고집적화에 유리하다. 마이크로비아의 형성기술은 크게 네 가지 범주로 구분할 수 있는데, Photovia process, Plasma-via process, Laser-via process, Paste-via process 등이 있으며, 일부 폴리이미드 필름을 사용하는 기술을 제외하면 마이크로비아의 크기는 100~150㎛, 미세도선의 선폭은 75~100㎛ 수준을 보이고 있다. 전도성 페이스트로 비아를 충진하는 방법은, 주로 Ag, Cu 금속분말을 열경화성 수지와 혼합하여 제작된 페이스트를 스크린 인쇄방법 등을 이용하여 레이저에 의해 형성된 마이크로비아를 충진하는 방법이다. 다수의 일본업체들은 이미 상당 수준의 층간접속 페이스트 기반의 HDI 기술을 개발하여 제품을 출시하고 있다. 대표적인 기술로서 Matsushita의 ALIVH, Denso의 PALAP, DNP의 B2it 등을 들 수 있으며, 각 기술별로 고유의 특징을 보유하고 있다. 대표적인 페이스트 기반 HDI 기술의 공정도를 그림 1에 나타내었다.

그밖에 전도성 비아 페이스트를 사용하는 공정으로서 UniCap의 MfVia, CTS의 ViaPly, Toranaga의 Or

met, Parelec의 PARMOD, Namics의 Unimec 등이 있으며, Ag, Cu, Cu/

Sn, Pd 등을 이용한 페이스트를 주로 사용하고 있다.

비아 Interconnection용 소재의 개발동향은 페이스트  타입으로 금속 자체의 도전성 및 열전도도에 가까운 수준의 특성을 얻고자 하는 방향으로 진행되고 있다. 전문 페이스트 업체들은 각자의 축적된 기술을 활용하여 Thermal 비아용 Via plug 소재, 층간접속용 비아필링 소재 등을 출시 판매하고 있다. 초기의 페이스트 타입의 비아는 Cu, Ag 등 전도체 분말을 에폭시 등의 열경화형 페이스트와 혼합하여 제작된 것들이었다. 이는 레이저나 드릴에 의해 형성된 비아 홀에 전도성 페이스트가 채워지고 가압적층에 의해 층간 접속이 이루어지는 형태이다. 그러나 이 경우 전도패스의 형성은 입자간 접촉에 의해서만 이루어지고, 특히 비아와 접촉되는 동박과의 계면에서 바인더 소재에 의해 접속이 영향을 받기 때문에 우수한 전도성을 확보하기 어렵고, 접속부의 신뢰성을 확보하기 어려운 단점이 있다.

타입으로 금속 자체의 도전성 및 열전도도에 가까운 수준의 특성을 얻고자 하는 방향으로 진행되고 있다. 전문 페이스트 업체들은 각자의 축적된 기술을 활용하여 Thermal 비아용 Via plug 소재, 층간접속용 비아필링 소재 등을 출시 판매하고 있다. 초기의 페이스트 타입의 비아는 Cu, Ag 등 전도체 분말을 에폭시 등의 열경화형 페이스트와 혼합하여 제작된 것들이었다. 이는 레이저나 드릴에 의해 형성된 비아 홀에 전도성 페이스트가 채워지고 가압적층에 의해 층간 접속이 이루어지는 형태이다. 그러나 이 경우 전도패스의 형성은 입자간 접촉에 의해서만 이루어지고, 특히 비아와 접촉되는 동박과의 계면에서 바인더 소재에 의해 접속이 영향을 받기 때문에 우수한 전도성을 확보하기 어렵고, 접속부의 신뢰성을 확보하기 어려운 단점이 있다.

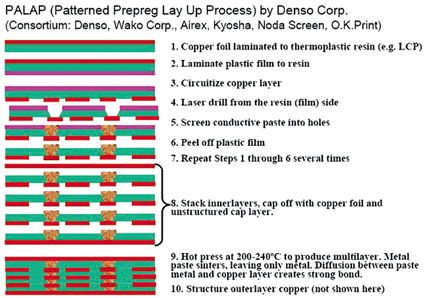

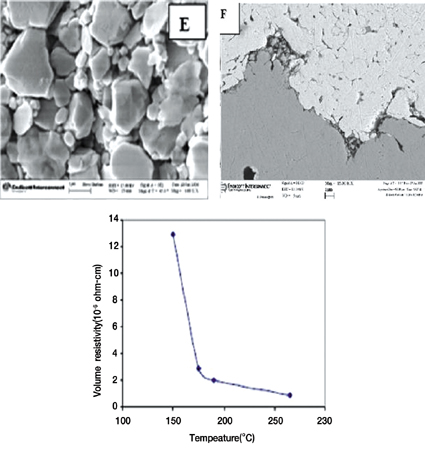

복합체를 이루고 있는 폴리머 소재가 금속의 특성을 크게 저하시키기 때문에 이를 개선하고자 하는 연구가 이루어지고 있다. 그 중 하나로서 Sintered nano-Ag를 이용하는 방법이 매우 주목할 만한 기술이며, 이미 상당 부분 연구가 진척되고 있는 것으로 파악된다. 나노 분말 단독으로 사용되기 보다는 마이크로 입자와 나노 분말을 함께 혼합하여 사용하는 방법이 연구되고 있다. 그림 2는 Endicott Interconnect 사에서 발표한 자료로 80nm 크기의 나노 Ag 입자를 마이크로 입자와 혼합하여 만들어진 페이스트의 열처리 전후의 모습을 나타낸다. 열처리 후 단면사진(F)으로부터 페이스트와 동박의 접속이 잘 이루어지고 있음을 확인할 수 있다. 또한, 이 방법으로 300℃ 이하의 열처리 후에도 페이스트의 체적저항(volume resistivity)을 2×10-5 Ωcm이하로 낮출 수 있는 장점이 있다. 한편 저융점 금속 합금을 이용하여 비교적 저온에서 금속성 접합이 이루어지도록 하는 기법도 연구되고 있다. Ag 및 Cu 등은 융점이 높아서 가압적층 후 동박과의 금속결합적 접속이 일어나지 않는다. 따라서 여기에 Sn과 같은 저융점 금속을 복합하여 열처리 후 동박과 금속접합을 이룰 수 있도록 하는 연구가 활발히 진행되어 Tatsuta 및 Fujikura 등에서는 이미 상품을 출시하고 있다. 특히 Fujikura에서 출시한 전기전도성 접착제 및 페이스트 소재인 DOTITE series는 열처리 시 금속결합과 수지접합이 동시에 일어나도록 재료를 설계하는 한편, 열처리 후 융점이 이동하는 소재의 특성을 이용하여 열 이력에 의해 전도성이 저하되지 않도록 접속 신뢰성을 향상시키는 기술을 적용하였다. 이 소재는 저융점 금속합금입자와 준 안정상에 의한 융점변화 특성을 가진 합금입자를 혼합하여 수지 바인더와 함께 페이스트화하는 방법으로 만들어진다. 그림 3에 금속결합이 이루어지는 개략도와 열처리후 단면구조를 나타내었다. 단면사진으로부터 동박과 비아 접속층 사이의 계면에 금속접합 상이 이루어져 있는 것을 확인할 수 있다.

3. 본딩필름을 이용한 고집적 공정기술 층간용 접속용 소재는 인쇄회로 기판위에 반도체 등을 얹어 플립칩용 BGA 패키지 등의 제품을 제작하기 위한 소재로써 본 기술을 이용하면 소재의 압착을 통하여 다층화가 가능하고, 도금에 의해서 선로를 형성함으로서 미세 선폭을 지닌 회로를 구현하는 특성을 가진다. 층간 접속소재는 박형의 미세 선로 구현을 통한 기능성 인쇄회로 기판 구현이 가능하다. 층간 접속 소재의 구현은 일반적으로 앵커를 형성하는 화학 공정 및 형성된 앵커에 Pd 촉매 등을 이용하여 무전해 도금을 행하고 에칭을 통해서 미세 라인을 형성하는 공정기술로 구성된다. 그림 4에는 층간 접속 필름을 이용한 기판 제작 공정도를 나타내었다.

층간용 접속용 소재는 인쇄회로 기판위에 반도체 등을 얹어 플립칩용 BGA 패키지 등의 제품을 제작하기 위한 소재로써 본 기술을 이용하면 소재의 압착을 통하여 다층화가 가능하고, 도금에 의해서 선로를 형성함으로서 미세 선폭을 지닌 회로를 구현하는 특성을 가진다. 층간 접속소재는 박형의 미세 선로 구현을 통한 기능성 인쇄회로 기판 구현이 가능하다. 층간 접속 소재의 구현은 일반적으로 앵커를 형성하는 화학 공정 및 형성된 앵커에 Pd 촉매 등을 이용하여 무전해 도금을 행하고 에칭을 통해서 미세 라인을 형성하는 공정기술로 구성된다. 그림 4에는 층간 접속 필름을 이용한 기판 제작 공정도를 나타내었다.

층간 접속 소재를 개발에는 세라믹-폴리머 컴포지트 소재 기술이 활용된다. 일반적으로 BT(Bismaleid Triazine) Resin과 같은 고내열성 폴리머 소재에 SiO2 분말 소재를 컴포지트화해서 테입으로 제작한 소재가 활용되며 과망간산 칼륨에 용해되어 앵커를 형성할 수 있는 특성을 소지한 유기 폴리머 소재 첨가제를 혼합한 조성을 이용한다.

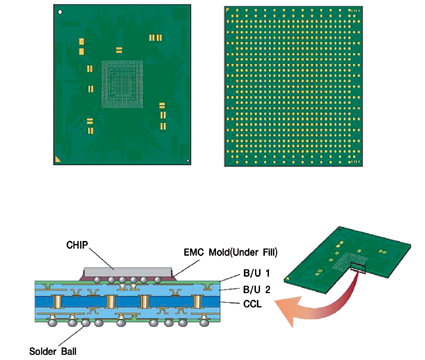

그림 5에서는 층간 접속 소재가 사용되는 예로서 CPU 및 칩셋 등에 주로 적용되는 Flip-chip BGA PCB의 구조를 나타내었다. 활용되는 주요 소재는 High Tg FR4 등의 절연 소재와 회로형성용 전해 동박으로 구성된 CCL에 절연 접착시트인 층간 접속 필름이 이용되었다. FC-BGA는 일반적으로 6층의 구조를 가지며 최종제품의 두께는 0.8~1.0mm 이며 회로폭/간격은 25/25 μm, BGA의 볼의 폭은 0.2mm으로 매우 미세한 구조의 특징을 지니고 있다. 층간 접속 필름은 기존의 에칭 공정에 비해 장점을 지니고 있다. 에칭 기술을 활용한 PCB 제품은 후막의 동박을 사용하기 때문에 미세라인을 구현하는데 한계가 있다. 이러한, 기존 기술은 코아 소재를 중심으로 빌드업을 행하는 공정 기술을 이용하기 때문에 박형 기판을 제작하는 것은 매우 어려운 상황이다. 최근에 휴대 전자기기가 얇아지면서 박형 회로 기판 기술은 층간 접속 필름을 기판을 이용하여 극박 회로를 구현하는 기술로서 층간 접속 필름에 대한 관심이 증폭되고 있다.

전자기기가 얇아지면서 박형 회로 기판 기술은 층간 접속 필름을 기판을 이용하여 극박 회로를 구현하는 기술로서 층간 접속 필름에 대한 관심이 증폭되고 있다.

층간 접속 기술은 반도체 칩 부품을 기판 위에 혹은 회로 기판 내에 매몰시키려는 SOP(System on package) 기술의 발전과 함께 패키지용 핵심 소재 기술로서 관심이 증폭되고 있다. 패키지용으로 칩을 내장하기 위한 소재로서는 공정 후에 휨 발생의 공정 상 문제점을 최소화하는 것이 필요하다. 이러한 공정 결함을 줄이기 위해서 CTE(Coefficient of temperature expansion)의 편차를 줄이기 위한 Low CTE 소재 개발이 지속되고 있다.

최근에 유럽 및 일본 등에서는 RoHS 규제 등과 같은 정책을 통해 전자 소재의 친환경화를 추진 하고 있다. 이에 따라서 접속 소자용 소재에서도 소재의 물성을 고온화 하는 것으로 개발이 진행되고 있다. 솔더링 소재인 납에 대한 규제로 비연계를 사용하면서 리플로우 온도가 증가되었으며 사용되는 인쇄회로 기판 소재 역시 고온에서 절연기판으로서의 물성을 유지하기 위해 High Tg 특성을 지닌 소재의 개발이 요구되는 상황이다. 난연성을 부여 하기위해 회로기판소재에서 첨가하는 소재가 할로겐족 원소의 하나인 브롬계 화합물인데, 이 화합물들이 최근 발암 및 유전적 돌연변이를 일으키는 환경 호르몬이라는 지적에 할로겐-프리 소재가 적용되고 있다.

하고 있다. 이에 따라서 접속 소자용 소재에서도 소재의 물성을 고온화 하는 것으로 개발이 진행되고 있다. 솔더링 소재인 납에 대한 규제로 비연계를 사용하면서 리플로우 온도가 증가되었으며 사용되는 인쇄회로 기판 소재 역시 고온에서 절연기판으로서의 물성을 유지하기 위해 High Tg 특성을 지닌 소재의 개발이 요구되는 상황이다. 난연성을 부여 하기위해 회로기판소재에서 첨가하는 소재가 할로겐족 원소의 하나인 브롬계 화합물인데, 이 화합물들이 최근 발암 및 유전적 돌연변이를 일으키는 환경 호르몬이라는 지적에 할로겐-프리 소재가 적용되고 있다.

4. 결론

페이스트 기반의 다층접속 나노소재 및 층간 접속 필름을 이용한 고집적 공정기술에 대한 주요 기술동향에 대하여 간략히 고찰하였다.

나노소재를 접속소재로 활용하기 위하여 더욱 향상된 분산기술과 고기능 고분자 소재 및 공정기술의 추가 개발이 요구되며, 다양한 기판재료에 알맞은 독자적인 접속소재의 개발이 필요하다. 또한 환경규제에 적절히 대응할 수 있는 특성을 가지도록 지속적으로 소재 특성 향상을 추진할 필요가 있다. 층간 접속 필름의 경우에 세라믹 - 폴리머 컴포지트 소재가 활용되고 있으며, 극박의 회로 패턴의 구현이 가능한 장점을 지니며, 친환경의 요구에 Low CTE 및 할로겐 프리 소재의 개발이 절실히 요구되고 있다.

(a)ALIVH

(b)PALAP

(c)B2it(Buried Bump Interconnection Technology)

그림 1. 대표적인 페이스트 기반 층간접속비아 형성기술

(출처 : ‘HDI Trends and Developments’,

CircuiTree Magazine, May 2006; JPCA Show 2007)

그림 2. Nano-micro filled silver based conducting adhesives sintered at the temperature below 300℃

그림 3. Fujikura Kasei의 층간접속용 페이스트의

원리 및 열처리후 단면구조

(출처 : Fujikura Kasei brochure, JPCA Show 2007)

그림 4. 층간 접속 필름을 이용한 기판의 제작 기술

그림 5. Schematic of cross section and bonding pad side of FC-BGA

강남기

강남기

연세대학교 금속공학과 박사

전자부품연구원 전자소재패키징연구센터 수석연구원

기사를 사용하실 때는 아래 고유 링크 주소를 출처로 사용해주세요.

https://www.cerazine.net