다기능 세라믹 박막의 내장화 기술

강종윤 한국과학기술연구원 박막재료연구센터 선임연구원

1. 서론

최근 휴대기기의 경량화과 고기능화, 복합화의 추세에 따라 전자 회로의 고밀도 실장, 고속화의 요구가 점점 커지고 있다. 고밀도 실장을 위해 능동소자와 수동소자의 크기를 작게 하는 연구는 각 부품 회사를 중심으로 활발하게 진행되어 왔지만 날로 가속화되는 전자 기기의 발전 속도에 맞추기 어려운 실정이다. 현재 2차원적인 반도체 및 이동 통신 소자의 집적도를 높이기 위해 새로운 기술적 제조방법들에 대한 연구가 활발하게 진행되고 있다. 이 중 집적도 향상을 위해 현재 가장 주목 받고 있는 기술이 3차원 접속 기술을 통해 칩의 집적도를 높이는 것인데, MCM (multi chip module)과 적층패키지 기술 등이 휴대용 전자제품과 고성능제품 등에 많이 적용되고 있는 3차원 패키징 기술의 하나이다. 또한 소자의 집적도를 높이는 요구와 함께 다양한 디바이스들, 즉, 메모리, LIS로직, RF, MEMS 또는 Sensor 그리고 optical device등과 서로 다른 특성과 기능의 칩들을 하나의 마이크로시스템으로 제조하는 기술들도 요구되고 있다.

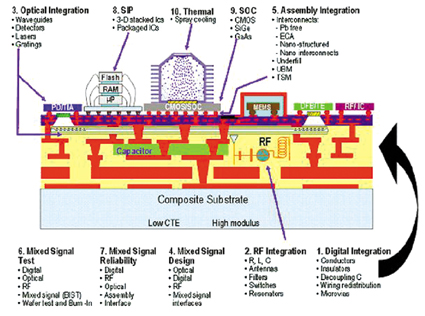

SoP (System on Package)는 SoC(Sytem on Chip), SiP(System in Package) 와 함께 컴퓨터, 통신, 가전, 바이오-전자 등의 기능을 하나의 패키징 또는 모듈에 통합할 수 있는 기술이다. 이는 짧게는 마이크로스케일로 길게는 나노스케일로 시스템 레벨 부품의 패키징 통합을 통해 소형화를 달성하는 것을 목적으로 하며, 그림 1과 같이 3차원으로 기판 내에 R, L, C 수동 소자 비롯하여 능동 소자 칩 등을 내장하고 기판을 적층하는 방법에 대한 기술적인 연구개발이 활발하게 진행되고 있으며, 더불어 다수의 복합 기능 소자가 내장된 기판의 개발 필요성 또한 높아지고 있다. 따라서, 수동소자, 능동소자, 복합소자의 기판 내 구현을 가능하게 하기 위해 필수적인 기능성 세라믹 박막의 내장화 기술의 개발 필요성이 크게 부각되고 있다.

2. 연구 개발의 필요성 휴대기기에서 수동소자와 능동소자의 비율은 약 8 : 2로 수동소자의 내장화 기술은 실장 면적 감소 측면에서 그 파급 효과가 매우 크다고 할 수 있다. 또한, 전체 수동소자 중 60% 비중을 차지하고 있는 콘덴서를 내장화 할 경우 전자부품의 실장 면적 감소에 막대한 효과를 가져 올 수 있다. 반도체 소자의 경우, 주로 Si 기판 다층화를 통해 소자의 집적화를 구현하며, 통신 소자의 경우, 적층 세라믹 기판, 적층 PCB 기판, 기타 적층 폴리머 기판 기술 등의 3차원 집적화 기술을 이용하여 소자의 집적화 및 소형화를 구현한다.

휴대기기에서 수동소자와 능동소자의 비율은 약 8 : 2로 수동소자의 내장화 기술은 실장 면적 감소 측면에서 그 파급 효과가 매우 크다고 할 수 있다. 또한, 전체 수동소자 중 60% 비중을 차지하고 있는 콘덴서를 내장화 할 경우 전자부품의 실장 면적 감소에 막대한 효과를 가져 올 수 있다. 반도체 소자의 경우, 주로 Si 기판 다층화를 통해 소자의 집적화를 구현하며, 통신 소자의 경우, 적층 세라믹 기판, 적층 PCB 기판, 기타 적층 폴리머 기판 기술 등의 3차원 집적화 기술을 이용하여 소자의 집적화 및 소형화를 구현한다.

가까운 시일에 반도체 및 통신, 그리고 기타 바이오 기능 등을 함께 구현하기 위한 다수의 복합 소자 집적화가 가능한 복합 적층 기판의 출현을 앞두고 있고 이에 따라 각종 기판에 다양하게 적용 가능한 기능성 세라믹 박막의 내장화 기술 개발이 필수적으로 이루어져야 할 것이다. 이를 위해서는 기존의 세라믹 박막의 공정 온도 (600℃ 이상) 개념과는 전혀 다른 저온 공정 온도 (350℃ 이하)에서 박막을 형성하고 그 기능을 발휘하도록 할 수 있는 원천 기술 개발이 절실히 필요하다. 현재까지 기능성 세라믹 박막은 고온에서 증착 또는 열처리함으로써, 결정화를 이루었고, 이와 같은 공정 조건하에서 우수한 특성을 갖는 세라믹 박막의 구현을 위한 연구 개발이 전개되어 어느 정도 괄목할 성과를 이루었다. 그러나 이 경우, 세라믹 박막의 구현은 극히 제한된 공정 조건(특히 공정 온도의 제한이 매우 높음)에서만 가능하며, 기판의 선택도 자유롭지 못하다는 한계가 뒤따른다.

무소성 저온 세라믹 적층 기판은 기존의 세라믹 기판과는 달리 소성 수축 공정을 거치지 않고 소결된 나노 세라믹 파우더를 초고밀도 충진하고, 이에 저손실 resin을 함침하여 기판을 성형 하고자 하는 기술로 350℃ 이하의 공정 온도에서 그 개발이 이루어지도록 함으로써, 이종 소재간의 상호 불필요한 혼합을 최대한 억제하여 고성능 기판 개발이 가능할 것으로 예측되는 미래 원천 기판 기술이다.

이와 같은 무소성 저온 세라믹 적층 기판의 경우, 기존 고온 공정 기술로는 집적화를 위한 기능성 박막의 내장화가 현실적으로 불가능하다. 따라서, 350℃ 이하의 저온 공정 조건에서 기능성 세라믹 박막을 형성할 수 있는 새로운 원천 기술의 개발이 절실히 요구되며, 이와 같은 기술이 개발이 성공적으로 이루어질 경우, 각종 능수동 소자 및 복합 소자의 집적화 기술에 새로운 패러다임을 가져올 것이다.

3. 국내·외 관련기술의 현황

가. 다기능 세라믹 박막 내장화 기술의 국외 관련 기술 현황

다기능 세라믹 박막의 내장화 기술은 주로 embedded decoup

ling capacitor 기술을 중심으로 연구 개발이 진행되고 있다. 기판의 크기를 최소화하고 성능을 극대화하기 위해 decoupling capacitor를 기판 내에 embedded하고자 하는 노력이 지속적으로 진행되어 왔다. 저가의 유기 재료는 요구되는 정전용량 밀도를 얻기 힘들며, 이를 극복하기 위해 세라믹-폴리머 nanocom

posite에 관한 연구가 다양한 연구 그룹에서 지난 10년간 지속적으로 활발히 진행되어 최대 약 10 nF/cm2 정도의 정전용량 밀도를 얻는데 성공하였다. 그러나 nanocomposite 기술은 미래의 고속 프로세서에 적합한 임피던스에 도달하기에는 어려울 것으로 전망된다. 반면, 300~1000 정도의 유전상수를 갖는 BT 또는 BST는 5 μF/cm2의 정전용량 밀도를 가질 수 있으며, 따라서 고속 프로세서에 적합한 임피던스 요구 사항을 만족시킬 수 있을 것으로 전망된다.

현재 미국 또는 세계 선진 연구 기관에서는 1μm 이하의 두께를 갖는 embedded 캐패시터용 세라믹 박막에 관한 연구를 활발히 진행하고 있다. 1990년대 초반부터 미국의 연구소/기업 연구소를 중심으로 내장형 수동소자에 대한 연구가 시작되어 유럽, 일본, 한국도 그 연구를 진행하고 있다. 특히 내장형 콘덴서는 연구 그룹별로 다량한 소재, 막형성 방법을 선택하여 접근하고 있으나 단품 콘덴서의 특성 및 안정성을 구현하는데는 아직 한계가 있는 실정이다. Embedded Capacitor 기술은 크게 Sheet Type과 Discrete Type, 그리고 Thin Film(박막) Type이 있으며 그 특징을 요약하면 표 1과 같다.

Sheet (또는 Planar) type의 Embedded Capacitor는 기존의 폴리머 lamination층의 물성을 개질하여 정전용량을 늘리려는 기술로서 Sanmina SCI社가 원천기술 ‘US 5079069, US 5162977’을 보유하고 있는 상황이며, 1990년부터 기판의 내층에 CCL(Copper Clad laminates) 형태의 Epoxy base의 FR-4로 구성된 BC2000재료 (εr=4.5)를 내장하여 Network board 의 Decoupling Capacitor용으로 사용하고 있으나, 용량 값의 부족으로 몇몇 Set 업체들만이 적용을 하고 있다[1]. 또한 모토롤라 연구소는 2002년에 ceramic-filled (barium titanate) photodielectric 물질을 개발하여 유전율 20 (@1.8GHz)을 구현하였으며 이를 이용하여 12㎛의 두께로 약 1.7nF/cm2의 capacitance density를 구현하는데 성공하였다[1][2]. 또한 3M은 barium titanate로 충진된 에폭시를 이용하여 최대 유전율 18을 얻었으며 4㎛두께에 4.65nF/cm2의 정전용량을 확보하였다[1].

Paste type의 Embedded Capacitor의 경우 BaTiO3와 Polymer resin으로 구성된 Paste를 인쇄기술을 이용하여 기판 내에 Discrete type capacitor를 구현하는 방법이다. 현재 많은 PCB업체가 샘플 평가를 진행 중이며 대표적으로 Dupont등의 업체들이 신뢰성 평가 진행을 완료한 상황이다.

최근 기술적 관심을 모으고 있는 Thin film(박막) Embedded Capacitor는 Sputter 및 Sol-Gel Process를 이용하여 PLZT(Pb,La)(Zr,Ti)O3, BaTiO3, BaSrTiO3를 기판에 증착하여 고용량의 Capacitance를 얻는 방법이 있으며 North Carolina State University와 Motorola社가 공동 연구개발 중이나 상용화에 대한 적용 검토는 아직 부족한 상태이며 350℃ 이하의 저온공정에서는 그 유전율이 현저히 떨어지는 단점이 있어 신규 재료에 대한 검토가 반드시 필요한 상황이다. Thin film(박막) Embedded Capacitor의 경우에는 Shinko, Hitachi, Fujitsu 등에서 양극산화법, Sol-Gel process, Sputter 등의 다양한 방법으로 기술 개발 중이나 마찬가지로 상용화에 대한 적용 검토는 아직 부족한 실정이다.

다기능 세라믹 박막의 내장화 기술은 기판 내에 다양한 기능을 부가시키고, 단위 면적당 실장률을 높이기 위해 미국, 일본, 유럽 등 선진 연구 개발 기관에서 현재 매우 활발한 연구 개발 동향을 나타내고 있다. 그 개발 동향은 응용 즉, 세라믹 박막 내장화 기술이 적용되는 기판 별로 연구 결과 수준 및 현황이 매우 다르다.

LTCC 등의 유전체 세라믹 기판의 집적화를 위한 세라믹 박막 개발은 기판에 따른 공정 제한 조건 (공정온도 900℃ 이하)이 까다롭지 않아 연구 개발 진척도가 높고 현재 산업화 수준에 이르고 있다. 또한, 주로 실리콘을 기반으로 하는 반도체 소자의 집적화를 위해 실리콘 기판을 주 타겟으로 하는 세라믹 박막 내장화 기술은 최근 500℃ 정도의 공정 온도 한계를 극복하는 방안으로 활발히 진행되고 있으나, 아직 초기 개발 단계 수준이다. 반면, 무소성 세라믹 기판 또는 PWB (Printed Wiring Board) 기판의 집적화를 위한 다기능 세라믹 박막의 연구는 아직 400℃ 이하의 공정 온도의 한계를 극복하지 못하여 연구 도입기 단계에 머물러 있는 실정이다. 다기능 세라믹 박막의 내장화 기술은 소자의 소형화 및 실장률 향상을 위한 반도체 집적화 기술, 시스템 및 소자 패키징 기술 등의 핵심 기술로 고려되고 있으며, 다양한 기판 재료에 응용하기 위해 350~400℃ 이하의 공정 온도에서 기능성 박막의 증착 및 결정화가 이루어져 박막의 특성을 발휘할 수 있어야 한다.

센서 및 주파수 가변소자 등에 응용 가능한 압전체 등 강유전체 박막의 저온 공정 내장화 기술은 전세계적으로 아직 초기 단계에 머물러 있다. 현재, 폴리머 기판 등에 증착된 압전 박막의 개발 결과가 발표된 적 있으나, 그 수준이 아직 응용 단계에 못 미친다. 캐패시터용 유전체 세라믹 박막과 더불어 압전체 등 강유전체 박막의 저온 공정 실장화 기술은 그 기술의 개발 필요성이 매우 높고, 기술적 사회적 효과가 매우 높은 것으로 고려되어, 전세계적으로 핵심 개발 대상 기술로 고려되고 있다.

나. 다기능 세라믹 박막 내장화 기술의 국내 관련 기술 현황.jpg) 미국, 일본 등의 선진 개발 국가에서 세라믹 박막의 저온 공정 내장화 기술은 초기 개발 단계이지만, 많은 연구 개발 기관에서 매우 활발히 진행되고 있는 반면, 국내의 기술 개발은 매우 국한적으로 진행되고 있다. 최근에, embedded 캐패시터용 유전체 박막의 연구 개발 결과가 보고된 적 있으나, 아직 상용화 단계에 이르지 못하고 있다. 국내의 기능성 세라믹 박막은 주로, 기판의 공정 온도나 결정화 온도가 매우 높은 (600℃ 이상) 공정 조건에서 기능성 세라믹 박막의 우수한 특성을 구현하는 방향으로 연구가 진행되고 있다. 따라서, 무소성 세라믹 기판의 집적 내장화 소재로 적용하기에 공정온도라는 큰 장애가 있고 현재까지 이러한 소재 기판에 적용 가능한 기능성 박막의 연구 결과는 찾아보기 힘든 실정이다.

미국, 일본 등의 선진 개발 국가에서 세라믹 박막의 저온 공정 내장화 기술은 초기 개발 단계이지만, 많은 연구 개발 기관에서 매우 활발히 진행되고 있는 반면, 국내의 기술 개발은 매우 국한적으로 진행되고 있다. 최근에, embedded 캐패시터용 유전체 박막의 연구 개발 결과가 보고된 적 있으나, 아직 상용화 단계에 이르지 못하고 있다. 국내의 기능성 세라믹 박막은 주로, 기판의 공정 온도나 결정화 온도가 매우 높은 (600℃ 이상) 공정 조건에서 기능성 세라믹 박막의 우수한 특성을 구현하는 방향으로 연구가 진행되고 있다. 따라서, 무소성 세라믹 기판의 집적 내장화 소재로 적용하기에 공정온도라는 큰 장애가 있고 현재까지 이러한 소재 기판에 적용 가능한 기능성 박막의 연구 결과는 찾아보기 힘든 실정이다.

4. 연구 개발 방법

무소성 세라믹 기판 및 폴리머 기판 등에 응용 가능한 350℃ 이하의 공정 온도를 갖는 다기능 세라믹 박막의 내장화 기술은 다음과 같은 개발 내용을 목표로 하고 있다.

저온 공정 (350℃이하) 세라믹 강유전체 박막 개발저온 공정 마이크로파 강유전체 박막 저온 공정 압전 박막·유전율 : 300 이상

.유전손실 (tanδ) : 0.02 이하 at 10 GHz

.tunability : 10% 이상

.공정온도 : 350℃이하 ·압전정수 (d33) : 40 pC/N 이상

.잔류분극 : 10 μC/cm2 이상

.fatigue : 106 cycle 이상

.공정온도 : 350℃ 이하 저온 공정 (350℃이하) 세라믹 유전체 박막 개발저온 공정 고유전율 세라믹 유전체 박막저온 공정 저유전율

저손실 세라믹 유전체 박막·유전율 : 75 이상

.유전손실 (tanδ) : 0.01 이하 at 10 GHz

.누설전류 : 1㎂/cm2 이하 at 3V

.공정온도 : 350℃ 이하 ·유전율 : 8.5

.유전손실 (tanδ) : 0.01 이하 at GHz

.유전박막 층수 : 5층

.공정온도 : 350℃ 이하

저온 공정 강유전체 박막 개발을 위해 Continuous Composi

tion Spread법 등을 이용하여 BST 조성 및 bismuth-based layered structure 계 등의 신조성 개발을 진행할 예정이다. 이 방법은 이분계 또는 삼분계 등 상이한 조성 타겟을 동시 sput

layered structure 계 등의 신조성 개발을 진행할 예정이다. 이 방법은 이분계 또는 삼분계 등 상이한 조성 타겟을 동시 sput

tering하여 전범위 조성 특성 고찰함으로써 최적 조성 개발을 위한 공정 시간 및 비용 단축할 수 있을 것으로 기대된다.

또한, 저온공정 고유전 세라믹 유전체 박막의 개발을 위해 Sm2TimO7, Bi(Zn,Mg)NbO3 등의 박막 재료 개발 및 이에 적합한 공정 개발이 이루어질 것이고, 저유전율 저손실 유전체 박막의 경우, Borate계와 Aluminate계 등의 조성을 기반으로 하는 저온공정 유전체 박막의 개발을 진행할 예정이다.

저온공정 기능성 박막의 개발을 위해서는 신조성 개발과 더불어 공정 개발이 필수적인데, 본 연구 개발에서는 증착 공정 및 후열 처리 공정 등에 있어 새로운 방법을 시도하여, 기능성 세라믹 박막의 결정성을 향상시키는 연구를 진행할 예정이다.

우선 증착 공정에 있어서는 박막 증착 에너지가 가장 높다고 알려진 Pulsed Laser Deposition (PLD) 공정과 더불어 일반적인 RF sputter에 부가적으로 DC bias를 인가함으로써 박막의 증착 에너지를 높이고 저온에 우수한 특성의 기능성 세라믹 박막의 구현이 가능하도록 할 예정이며, RF 또는 DC Plasma를 MOCVD와 겹합한 박막 증착 공정 등을 개발할 예정이다. 또한, 후열처리 공정에 있어서, 이 또한 공정 온도를 350℃ 이하에서 진행할 것을 목표로 하기 때문에 UV가 결합된 RTP (Rapid Thermal Processing) 그리고, 열처리와 더불어 DC bias의 인가가 가능한 DC bias tube furnace 등을 개발하여 저온 공정 기능성 세라믹 박막의 연구에 적용하고자 한다.

5. 결론

무소성 세라믹 기판의 내장 소자용 저온 공정 기능성 세라믹 박막의 내장화 기술 개발은 직접적으로 기판 내에 R, L, C 수동 소자의 내장화 및 IC 칩의 내장화를 구현 가능케 하여 고집적화 된 초소형 박형 소자 및 모듈 개발을 실현할 것으로 전망된다.

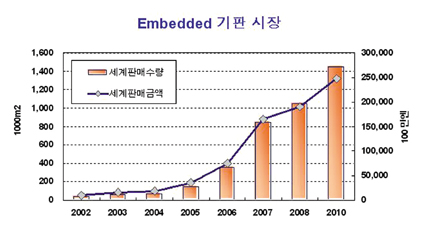

후지키메라 연구소의 2005 유망전자부품재료에 따르면 내장형 수동소자는 시장 규모면에서 그림 3에서 알 수 있듯이 2004년 기준 수량으로 70,000m2, 금액으로 약 1900억원, 2005년에 약 4000억원 이하로 아직 크지 않은 상태이다.

하지만 2010년 시장성장율 1300%로 반도체, 광 등을 포함하는 60여개의 재료 부품 중 상위 4위에 해당한다고 보고하며, 따라서 내장형 수동소자의 기술 개발시 예상되는 경제적 파급효과는 전자 산업 발전사에 큰 획을 그을 만큼 크다고 할 수 있다. 나아가, 내장형 수동소자를 기반으로 한 전자부품의 집적화 기술은 국내 전자부품의 국제적 경쟁력을 제고하여 세계적인 전자부품의 강국으로서의 입지를 확립할 수 있을 것이다.

저온 공정 기능성 세라믹 박막 기술의 개발은 공정 온도의 제한 조건이 크게 완화되므로 적용되는 기판의 선택도를 대폭 확대하여 다양한 기판에 적용 가능한 기술이다.

따라서, 무소성 세라믹 기판 뿐만 아니라, PWB 기판, flexible 디바이스용 폴리머 기판, Si 기판, LTCC 기판 등 다양한 기판의 내장화 기술로 적용 가능하므로 그 파급 효과가 매우 클 것으로 전망된다.

<참고문헌>

[1] Embedded components in printed circuit boards: a processing technology review / Jillek, W. ; Yung, W.K.C. ( International journal of advanced manufacturing technology, v.25 no.3/4, 2005, pp.350-360)

[2] Savic J, Croswell RT, Tungare A, Dunn G, Tang T, Lempkowski R, Zhang M, Lee T (2002) Embedded passives technology implementation in RF applications. Circuitree June:10-24

그림 1. 내장화 기술의 개념도

그림 2. CCS 공정도

그림 3. Embedded 기판 시장 전망

강종윤

강종윤

연세대학교 전기공학과 공학사

연세대학교 본대학원 전기공학과 공학석사

연세대학교 본대학원 전기컴퓨터공학과 공학박사

한국과학기술연구원(KIST) 학생연구원

한국과학기술연구원(KIST) 선임연구원

University of Birmingham Post-doc.

<본 사이트에는 표가 생략되었습니다. 자세한 내용은 월간세라믹스를 참조바랍니다.>

기사를 사용하실 때는 아래 고유 링크 주소를 출처로 사용해주세요.

https://www.cerazine.net