대면적 고정밀 LTCC 다층기판기술개발 동향 및 산업적 응용전망

박윤휘 삼성전기 수석연구원

유수현 삼성전기 수석연구원

1. LTCC 기술 및 응용제품

LTCC(Low Temperature Cofired Ceramics : 저온동시소성세라믹) 기술은 은(Ag), 동(Cu)와 같은 높은 전기전도성을 갖는 전극(electrode)을 다층 세라믹 사이에 내장할 수 있는 세라믹 기판 기술을 의미한다. 1960년 초반에 via라는 개념을 도입하여 개발된 다층 세라믹 기판은 원래 alumina를 기반으로 하여 GE(General Electric)사에서 지속 발전하여, 1970년대에는 microprocessor용 기판으로 대량 사용되었다. 이후 기판 가격에 대한 이슈가 대두되면서, alumina ceramic은 점차 organic 세라믹으로 대체되기 시작하여 최근에는 거의 자취를 감추었다. 1980년대 초반 RF(Radio Frequency) 응용제품에 대한 수요가 발생할 때, 많은 회사에서 alumina ceramic 다층기판을 사이즈 소형화를 위하여 적용하고자 하였으나, 내부전극으로 사용하였던 텅스텐(W) 및 몰리브덴(Mo)의 전기저항이 너무 높아서 RF 손실이 중요한 제품에 사용이 매우 제약되었다. 이를 타개하기 위하여 Hitachi에서 저온에서 소성하기 위한 아이디어로 alumina에 glass를 혼합하여 소성온도를 기존의 1500도에서 900도 이하로 낮추는 신기술을 발표하였다. 이 기술을 사용하면 매우 높은 전기전도도를 갖는 Ag나 Cu를 사용할 수 있게 되어서, RF에 세라믹 다층기판을 본격 적용할 수 있는 길이 열리게 된 것이다. 이후, Murata(村田제작소), Epcos 등에서 본격적으로 기술개발에 착수하여 1990년대 중반부터는 휴대폰에서 주파수를 선택하는 FEM(Front End Module)에 LTCC를 본격 채용하게 되었다. 이후 근거리 데이터 통신인 블루투스 및 무선랜 시장이 활성화 되면서, 소형화 RF 모듈에 대한 필요성이 증가되면서, IC를 실장한 LTCC 모듈이 개발 및 양산되어 최근까지 LTCC의 최대 응용처가 되고 있다. 이렇게 개발된 LTCC는 아래 표 1에서 보듯이 고유의 장점과 함께 여러 가지 단점도 동시에 가지고 있는 기술이다.

표 1. LTCC와 HTCC의 주요 물성 비교

LTCC HTCC

재료 glass + alumina alumina

소성온도 900도 이하 1400도 이상

전극재료 Ag, Au, Cu 등 低저항 전극 Mo, W 高저항 전극

비유전율 5~8 9.5

3점 곡강도 150~200MPa 300~400MPa

Young’s modulus 120~130GPa 300GPa

열팽창계수 3.5~5.5ppm/K 6.0~7.5ppm/K

열전도도 3~4W/mK 15~20W/mK

Via 위치 정밀도 0.05% 가능(무수축) > 0.2%

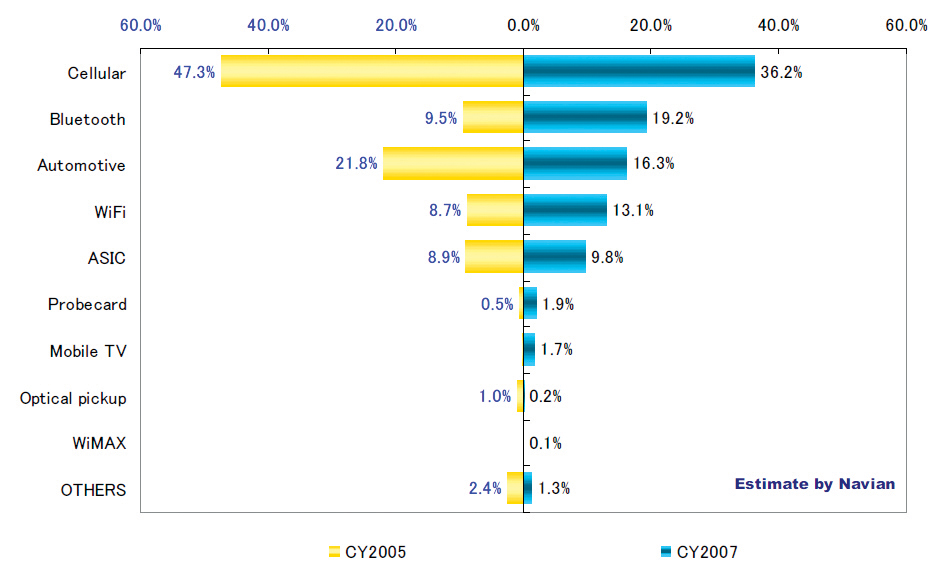

제품 측면에서 매력적인 장점으로는 낮은 전기저항, 낮은 열팽창계수, 낮은 비유전율, 그리고, 마지막으로 무수축소성에 따른 정밀한 via 위치구현 능력이다. 반면, 단점으로는 낮은 기계강도, modulus 및 열전도도를 들 수 있다. 앞에서 언급했듯이, 지금까지는 주로 낮은 전기전도도 및 열팽창계수를 이용한 소형 RF 제품에 주로 응용이 되어 왔으나, 낮은 강도, 열전도도 등 단점에 의하여 응용제품 확대에 한계를 느끼고 있다. 아래 그림 1은 LTCC의 주 응용제품을 나타내었다 [1].

그림 1. LTCC 적용 제품군과 Market Share

2. Probe Card용 대면적 세라믹 기판

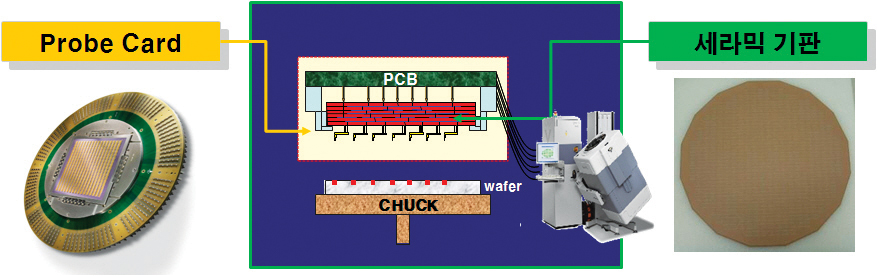

Probe Card는 반도체 wafer 상태에서 IC chip의 성능을 패키징 전에 사전 판별하기 위하여 사용되는 probing용 Jig이다. 최근 IC의 pad pitch가 지속적으로 감소하면서 기존의 pogo pin type의 card로는 대응이 불가능해면서, MEMS(Microelectromechanical Systems) 기술을 이용한 초정밀 pin을 이용한 probe card가 필요해 지고 있다.

또한, wafer 사이즈가 12″로 증가되면서, 사용되는 pin의 수가 30,000pin 이상으로 증가되고, 테스트하는 온도가 -20도에서 +120도 구간을 동시 측정해야 하므로, MEMS pin을 지지 고착시키는 기판으로 저열팽창, 대형 고정밀 세라믹이 필수적이 되었다. 그림 1에서는 MEMS Probe Card의 구조를 보여주고 있다. 이러한 Probe Card용 세라믹은 기존 RF용 세라믹과는 구조 및 요구사항이 표 1과 같이 상이하다. 특히, 12″의 대형 사이즈의 기판에 via hole의 위치가 +/- 300um 내에 위치해야 하는 조건을 만족시키는 것이 매우 어려운 과제로써, 지금까지 이를 해결하여 양산에 성공한 회사는 일본의 교세라가 거의 유일할 정도이다.

그림 2. Probe card와 세라믹 기판 [2]

표 2. RF용과 Probe Card용 LTCC의 비교

RF용 Probe Card용

기판 사이즈 4“ max. 4”~12”

제품 사이즈 2~10mm 기판 사이즈와 동등

두께 0.3~0.5mm 3~6mm

층수 5~20층 20~50층

총 via 수 수천~수만 30만~100만개

요구 via 위치 정밀도 0.2% 0.1%

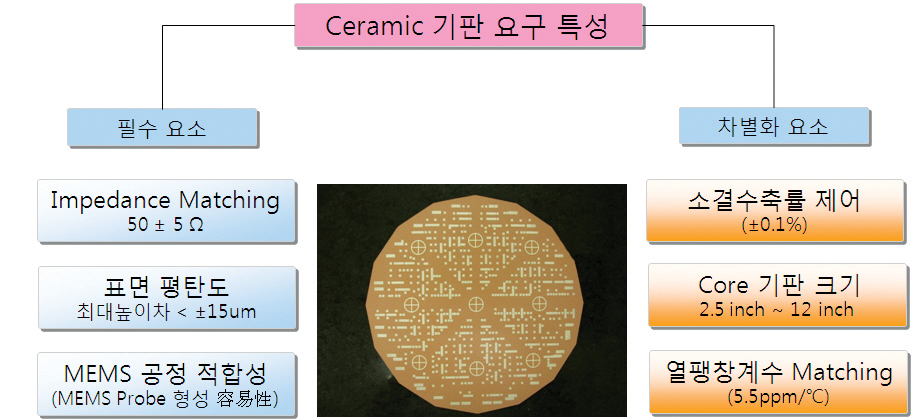

Probe Card용 Base 세라믹기판으로서, 세라믹 기판에는 그림3에 나타낸 것과 같은 몇 가지 주요한 특성들이 요구된다. 그러나 아래 요구특성들보다 더 큰 기술적 진입장벽은 최대 12인치 정도의 대형이면서도 매우 복잡한 기판을 1개의 통전불량(open/short circuit)도 없이 제조할 수 있느냐 하는 것이다. 세계적으로도 다층적층방식으로 세라믹기판을 제조하는 업체는 일본과 한국의 5개 정도에 불과하며, 주된 원인은 매우 높은 기술적 진입장벽 때문이다.

반도체 산업의 고집적화/고속화 추세에 따라 Probe Card내에 존재하는 Probe Pin의 개수도 점점 증가하여, 현재는 최대 25,000~30,000pin 정도의 고집적 Probe Card가 사용되고 있다. 이에 대응하여 최근 다층적층방식 세라믹기판(Multi-layer Ceramic Substrate)에서는 20층 이상, 500,000개 Via hole 이상이 필요한 상황이다. 이에 따라 세라믹기판을 여하히 1개의 통전불량도 없이 제조하기가 점점 어려워지고 있으며, 기본적인 세라믹 재료/공정기술을 계속 발전시켜야만 집적도 및 복잡성을 요구하는 반도체 산업의 추세에 대응할 수 있게 되었다.. 즉, 세라믹/금속재료, 성형(Casting), 적층(Lamination), 소결(Sintering) 등 세라믹기판 분야의 기본적인 기술의 성숙도가 점점 더 중요한 요소로 자리잡아가고 있다.

그림 3. Probe Card용 세라믹 기판의 요구특성

반도체 Maker 또는 Probe Card Maker들이 원하는 특성은 크게 필수요소와 차별화요소로 나누어 볼 수 있다. 필수 요소는 Impedance matching, 표면평탄도, MEMS 공정 적합성 등이 있으며, 이러한 특성들은 반도체 Maker 또는 Probe Card Maker들의 필수 요구사항이고, Probe Card세라믹 기판을 양산하는 업체는 대개 이에 필요한 요소기술들을 어느 정도 보유하고 있다. 반면 차별화 요소 기술은 최근 반도체산업의 추세에 따라 새로이 요구되는 기술로서, 소결수축률 제어를 통한 집적도 증가, 12인치 Wafer 대응 대형 세라믹기판, 고온/저온 동시 test를 위한 열팽창계수 matching 기술 등이 있다.

Impedance matching 특성은 세라믹 기판 내부에 내장된 각 Signal Line들의 Impedance가 ±10% 내의 오차로 관리되어야 한다는 것이다. 이는 최종 사용자인 반도체 Maker들의 EDS(Electrical Die Sorting)공정에 필요한 전기적 특성이다.

표면 평탄도는 일반적으로 ±15um 이하의 고저차로 관리되어야 한다. 반도체 Maker에서 EDS공정을 진행할 때, 모든 Probe Tip의 높이가 같을 것이 요구되지만, 세라믹 기판 표면의 높이 차를 완전히 0으로 만드는 것은 불가능하다. Probe Card Maker들은 Probe Card의 가압체결, Probe Pin의 높이조절 등의 방법으로 세라믹 기판의 높이차를 보정하여 대응하고 있다. 그러나 Probe Card Maker들의 방법은 높이 차를 ‘보정’해 주는 방법에 지나지 않기 때문에 애초에 세라믹 기판을 평탄하게 제조하는 것이 중요하다.

MEMS 공정 적합성이란 Probe Card Maker들의 다양한 Probe Pin 형성 공정에 대응 가능한 정도를 의미한다. Probe Card Maker들의 제조방법에는 Si Wafer MEMS 전사(F사, T사), 개별 Pin의 접합(K사, M사), 세라믹기판에 직접 Growth(M사) 등 다양한 방법이 있다. Probe Card Maker들의 공정에 따라 화학물질, 조립방식, 열이력 등이 모두 다르므로 이에 대응할 수 있는 세라믹 기판이 필요하다.

최근 반도체 산업에서의 Wafer 대형화, 고집적화, 고속화 추세에 따라 Probe Card용 세라믹 기판에도 새로운 특성들이 필요하게 되었다. 우선 메모리 반도체 공정에서 사용되는 Wafer는 대부분 12인치 기판이므로 12인치 Wafer에 대응할 수 있는 대형 세라믹 기판을 제조하는 기술이 필요하게 되었다. 12인치 세라믹 기판을 만들기 위해서는 성형, 적층, 인쇄, 소결 등의 거의 모든 세라믹 기판 공정에서 설비의 대형화 및 넓이(평면) 방향의 균일도를 보장할 수 있는 기술적 혁신이 필요하다.

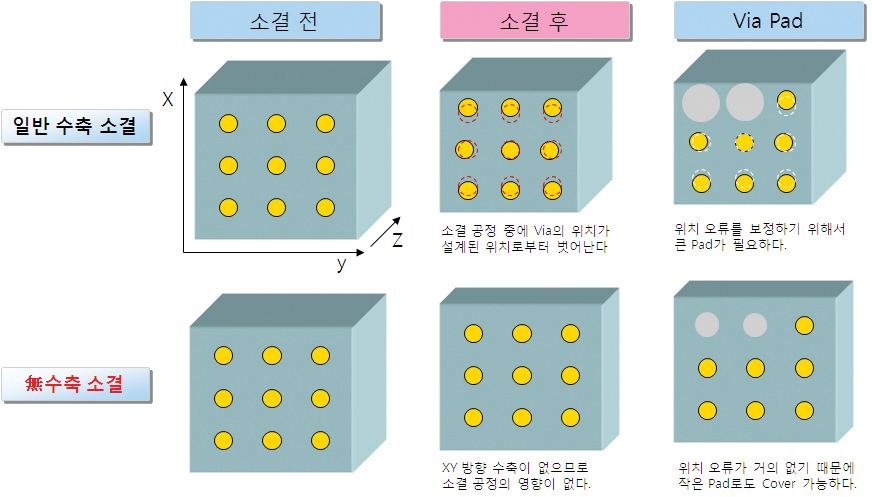

소결 수축률제어는 Probe Card 더 많은 Pin을 수용할 수 있게 하기 위하여 필요하다. 아래 그림에서와 같이 세라믹 기판의 소결 도중, 각 부분의 소결 수축률 편차 때문에 Via hole의 위치가 설계위치에서 미세하게 벗어나게 된다. 이를 보정하기 위하여 세라믹 표면의 Via hole Pad의 크기를 Via 크기보다 크게 제작한다. 이 때 Via hole Pad의 크기는 소결 수축률을 얼마나 잘 제어할 수 있는가에 달려있다. 소결 수축률 제어가 잘 되지 않으면 Via hole Pad의 크기가 커질 수밖에 없다. 기판 표면의 면적에서 Via hole Pad의 면적이 커지는 것은 기판에 수용할 수 있는 최대 Probe Pin의 수를 제한한다.

삼성전기는 독자적인 無수축소결기술을 개발/적용하여 소결 수축률 제어수준을 크게 낮추었다. 통상적인 해외업체의 소결 수축률 제어수준은 ±0.2% 정도로 최대 40,000개 정도의 Pin을 수용할 수 있는 반면, 삼성전기 무수축기술의 수축률 제어수준은 ±0.1% 수준으로 100,000 개 정도의 Pin까지 수용이 가능하다.

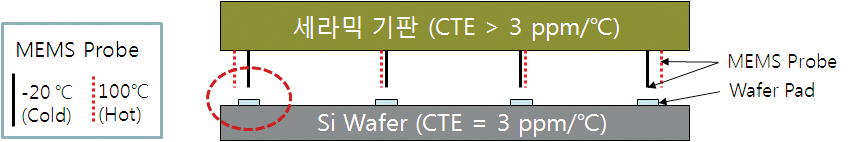

반도체 EDS공정에서 고온(~100℃), 저온(~-20℃) test를 한 장비에서 동시에 수행하기 위해서는 세라믹기판의 열팽창계수가 Si Wafer의 열팽창계수(~3.0ppm/℃)가 유사할 것이 요구된다. 현재까지 Probe Card용 세라믹 기판은 주로 α-Al2O3기반의 기판으로서 열팽창계수는 약 7.0ppm/℃(RT~400℃) 인데, 이 재질의 기판으로는 고온/저온 test의 동시 수행이 불가능하다.

따라서 반도체 Maker에서는 열팽창계수가 α-Al2O3에 비해서 작은 재료로 제작된 기판을 요구하고 있는 상황이다. K사(日)는 Mullite(3Al2O3·2SiO2, 5.0ppm/℃) 소재를 이용한 기판을 최근 개발하여 생산중에 있으며, 삼성전기는 LTCC(Low Temperature Cofired Ceramics)기술을 이용한 기판(Glass Ceramic, 5.5ppm/℃)을 개발하였다. 그러나, 재료가 바뀐 기판을 Probe Card Maker의 공정에 적용하는 문제가 아직 남아있으며, 다른 재료의 다른 물성으로 인한 다른 문제들에 대해 추가적인 검증이 필요한 상황이다.

표 3에는 현재 Probe Card용 세라믹의 참여 기업별 재료 및 적용 기술에 대한 현황을 예시하였다. 전통적인 세라믹 부품사업의 오랜 경력으로 인하여 세라믹 기술의 축적도가 높은 일본의 전문 세라믹 업체들이 대다수를 차지하고 있다.

그림 4. 소결 수축편차에 의해 요구되는 Via Pad의 크기

그림 5. 세라믹기판과 Si Wafer간 CTE(Coefficients of Thermal Expansion) 不일치에 의하여 MEMS Probe가 Pad에 접촉하지 못한 상황

표 3. 대형 세라믹 기판의 업체별 재료 및 기술 적용 현황

3. 향후 전망 및 과제

Probe Card용 세라믹의 요구조건은 앞으로 지속적으로 까다로와질 것으로 예상된다. 그 방향은 (1)50,000pin 이상의 다 pin 대응, (2)미세 pad 대응, (3)고속 테스트 주파수 대응이 될 것이며, 이를 효과적으로 해결하는 기술 및 업체가 시장을 주도해 나갈 것으로 보인다 [3]. 이 외에도 18″ 테스트에 대한 얘기도 최근 다시 언급되기 시작하는데, 이에 대한 양산은 2015년 이후나 가능할 것이라고 한다

이 분야의 시장은 세라믹 기반 기술이 발달한 일본에서 90% 이상 점유하고 있다. 국내에서 삼성전기 및 아이엠텍에서 이제 양산을 시작하는 단계에 와 있기는 하지만, 아직 수율, 양산성 및 납기 등에서 일본 업체에 뒤지고 있는 형편이다. 세계 반도체 점유율이 60% 이상을 점유하는 반도체 회사가 2개나 있는 국내 상황을 감안할 때, Probe card용 세라믹은 그 가치나 가능성이 앞으로도 매우 높다고 할 수 있으므로, 국내 세라믹업체의 지속적이고 체계적인 기술개발 및 양산품질 확보가 매우 절실하다고 사료된다.

참고문헌

[1] Advanced LTCC Technology 2008, Navian

[2] www.formfactor.com

[3] VLSI research 2011

박 윤 휘

박 윤 휘

- 서울대학교 무기재료공학사

- 서울대학교 무기재료공학석사

- 성균관대학교 전기전자공학박사

- 동양시멘트 중앙연구소 선임연구원

- 대우고등기술연구원 책임연구원

- 현 삼성전기 CDS 사업부 수석연구원

유 수 현

유 수 현

- 서울대학교 무기재료공학사

- 서울대학교 무기재료공학석사

- 서울대학교 재료공학박사

- 현 삼성전기 CDS 사업부 수석연구원

< 본 사이트에는 일부 내용이 생략되었습니다. 자세한 내용은 세라믹코리아를 참조 바랍니다.>

기사를 사용하실 때는 아래 고유 링크 주소를 출처로 사용해주세요.

https://www.cerazine.net